We had seen that Sequencing and Execution are two major activities to be carried out by the Control Unit. Sequencing is implemented by a State Machine Concept. The state machine logic is generally implemented using either Hardwired Combinational logic or Microprogramming. Execution is nothing but generating the necessary control signals.

In Chapter 12, we had detailed on the inputs to the Control Unit. We will further see the design requirements of a Hardwired and Microprogrammed Control Units.

Hardwired Control Unit

Hardwired Control Unit is implemented using Combinational Logic which includes Logic Gates, Decoders, Encoders and Counters. Very interesting that these simple circuits can rule the CPU!!

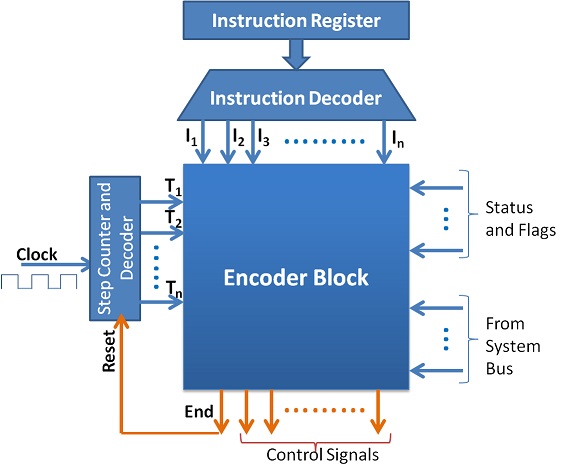

It is important to recall that each instruction has a defined set of machine cycles and each machine cycles has a set of defined steps primarily based on the instruction. The micro-steps are numbered as T1, T2,..Tn. These numbers are to be reset at the end of each machine cycle to pave way for the start of a next machine cycle. The Step counter cum decoder takes care of these micro-steps called timing states generation. The resetting of the Step Counter is triggered by the control unit as per the defined rules. All timing states need not be of the same duration. For example, a memory read cycle is longer than CPU internal operations and depends on the memory characteristics and bus availability. In such a case the Timing state gets extended in multiples of the CPU clock until the memory is done with read/write.

Figure 14.1 although looks similar to the one in chapter 13, few intricacies are added to understand the details of functioning. You may also see the detailing of how the decoded instruction is given as input to Control Unit.

Finite State Machine (FSM) i.e. the Encoder Block for hardwired control unit consists of:

- States

- Inputs

- Outputs

- Rules for computing outputs based on current state and inputs

Hardwired control unit design steps

The Logic Designer is expected to have written the RTL (Register Transfer Logic – a hardware definition language) description of each instruction execution in the ISA. Then the design is a three-step activity.

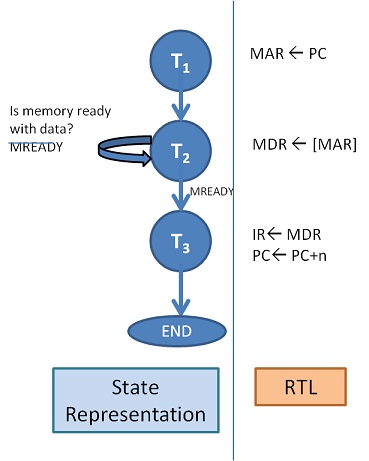

- Transform RTL into a state diagram for each machine cycle. This helps in determining which output signals should be asserted in each timing state.

- Assign state numbers to each timing state.

- Construct control unit to implement the state diagram.

Figure 14.2 is an example of the conversion of steps 1 and 2 for Instruction Fetch. On the right half is the RTL corresponding to the steps of the Instruction Fetch Cycle and the left is the state diagram. The overall number of control signals required for a CPU are very high and hence naming and numbering the signals with clarity is important.

Just for your imagination

Assume, a hypothetical CPU has 32 instructions, each instruction has 4 machine cycles and each machine cycle has 4 timing states to execute. The number of control signals we can visualize are 32x4x4=256. We need to add interrupt, trap servicing cycles, etc.

In reality, a CPU has 400+ instructions, 5 to 8 machine cycles and 4 to 8 timing states for each machine cycle for each instruction. The complexity is whoops!

Not only the deigner is expected to be knowledgeable but also very disciplined.

Similarly, the next step in the sequence is created and triggered. The next step could be a micro-step timing state, machine cycle or new instruction cycle. This is another complex logic.

Characteristics of Hardwired Control Unit

- Hardwired Control Unit provides the highest speed of execution

- Complex sequencing & micro-operation logic.

- Difficult to design and test

- Inflexible design

- Difficult to add new instructions

- RISCs are implemented with hardwired control. RISCs are said to be one instruction per clock cycle machines. Three-bus CPU structures, Register to Register operations and Hardwired control unit make it a reality.

- When the instructions set becomes complex like CISCs, the Hardwired Control Unit is unviable.

Microprogrammed Control Unit

Much of the difficulty of designing and implementing hardwired control units arises from the need to optimize the next state generation logic. If we could use memory to hold the state transition table for the control unit, we wouldn’t have to bother about optimizing any logic.

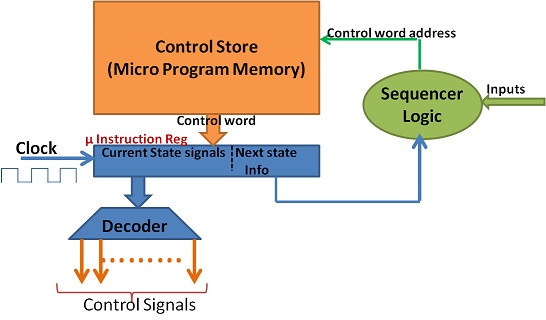

Alternatively, look for a memory-based control unit design, wherein the contents of a Control Memory location, when decoded, become the control signals for the current state. The current state is used as an "address" to access the Control Memory. The next state information for each state is also stored in the Control Memory Word. Control units that use this technique are called Microprogrammed Control Units. Thus Microprogrammed Control Unit is an alternative to Hardwired Control Unit implementation.

Figure 14.3 defines the components of a typical Microprogrammed Control Unit.

A microprogrammed control unit is implemented like another CPU inside a CPU. It executes microprograms stored in the Control Store. Before we proceed, let us see some vocabulary related to Microprogrammed Control Unit.

Control Store (Control Memory): A RAM or ROM that holds the truth table for a microprogrammed control system. The Control Store stores the Microprogram; also called Firmware or Microprogram Memory.

Control word (CW): The contents of a single location in the Control Memory. Practically represents the set of control signals of the current state; theoretically, each bit in a CW corresponds to one control signal. Control Word contains 1’s and 0’s corresponding to the active and nonactive control signals. One CW corresponds to one Microstep (Timing state) in the execution. A CW is also referred to as a Microinstruction.

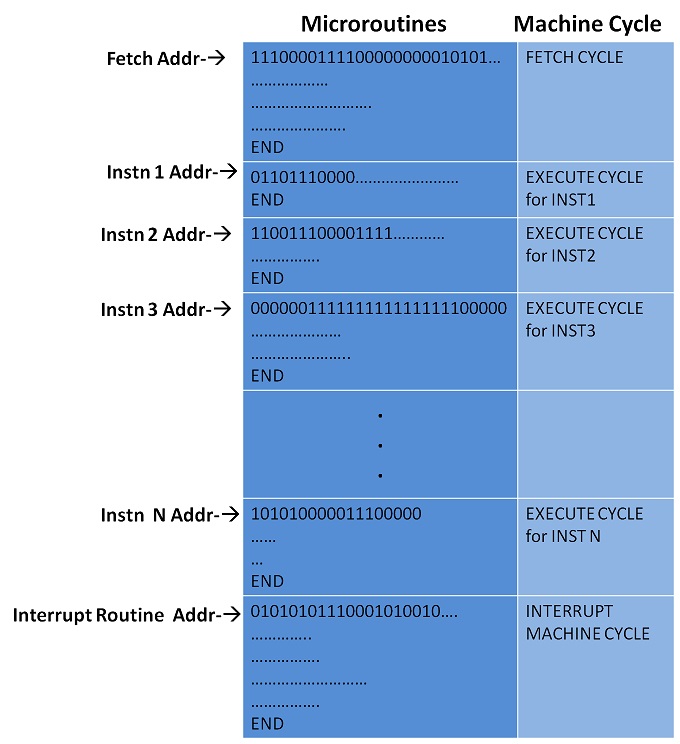

Micro program / Microcode/Micro routine: A set of Micro Routines make up a Microprogram for the CPU control unit. A Microcode or Micro Routine corresponds to a machine instruction or machine cycle. Every Micro Routine ends with an END statement to indicate the end of the machine cycle. Figure 14.4 depicts an example of the structure of a Control Store.

Microprogrammed Control Unit Design Steps

- As in the case of Hardwired Control Unit, Transform RTL into a State Diagram for each machine cycle of the ISA Instruction Set. This helps in determining which output signals should be asserted in each timing state.

- Assign state numbers to each timing state; Each state number will be a Control Word in the Micro Routine.

- Decide on the format of the Micro Instruction (Control Word). Here the width of the Control word and encoding method will have to be decided.

- The design logic for the Sequencer which generates the address to read the desired Micro Instruction. The Microprogram Sequencer generates address based on the current timing state signals, status from the bus, the END of each micro subroutine, and the branch address provided by the Micro Instruction.

Micro Instruction Format

A Micro Instruction specifies the control signals required in a particular timing state. It is the content of a location in the Control Store. It has two parts:

- a set of control fields that specify the control signals to be activated.

- an address field that contains the address of the next microinstruction to be executed.

This explicit address specification has the advantage that no time is lost in Micro Instruction address generation, but is wasteful of Control Memory space. The address fields can be eliminated from most of the instructions but not for branch instructions. An alternative way of generating address is by using a Micro Program Counter. Further, the encoding of the control fields reduces the width of the control memory.

Microinstruction width i.e the number of bits is decided by considering the following factors:

- Maximum number of simultaneous micro-operations that must be carried out in a timing state

- How the Control field information is encoded or represented

- The way microinstruction address is specified in the next address field

The microinstruction format is broadly classified as horizontal and vertical types based on the capability to accommodate encoding. The encoding possibilities are diagrammatically detailed in figure 14.5 and are self-explanatory. By now, it is clear that more the encoding less is the width of the Control Word. Thus Vertical formats require less width for Control Word while the horizontal format with least encoding demands larger width for Control Word.

Merits and Demerits of Microprogrammed Control Units

Merits

- Easy to design, write and modify

- Design architecture and microcode can be done in parallel

- Bugs in the control logic can usually be fixed by changing the contents of the RAM/ROM

- Can make use of internal registers more effectively

Demerits

- Speed is often slower than the computation in hardwired logic

- Parallelism in machine cycle is restricted

- When State Space explodes demands very large Control Store; When memory is costly, this becomes a serious limitation.

ISAs with very complex instructions benefit more from the Microprogrammed Control Unit. However, Microprogramming is out of favour when the entire Processor Chip is fabricated at one time, including Control Unit. In this scenario, the ability to do bug fixing by changing the Control Store is a less useful feature.

Nano programming

Nano means smaller than Micro. Instead of a microprogram decode the instructions and generate control signals, another level of control memory is used for decoding and generating control signals. This second-level control store is called Nano control memory and this method of generating control signals is called Nano Programming.

Nano control memory controls the hardware and contains nano instructions. The objective of nano programming is to reduce the total size of control memory and also have design flexibility in generating control signals. The design flexibility results from the loosening of the bonds between instructions and Hardware with two intermediate levels of control store rather than one.

The disadvantages of nano programming are:

- the two-level approach causes loss of speed due to extra memory access

- more complex control unit organization

Dynamic Programming

Dynamic Programming is another microprogramming technique implemented in a WCM (Writable Control Memory). It allows a systems programmer to dynamically change a processor’s instruction set by changing microprogram that interprets the instruction set. In principle, provide the same machine with multiple instruction set, tailored to special applications. Since the Control Memory contents are altered under program control, the name dynamic programming. Set-Top boxes used with television is a practical application and a good example.